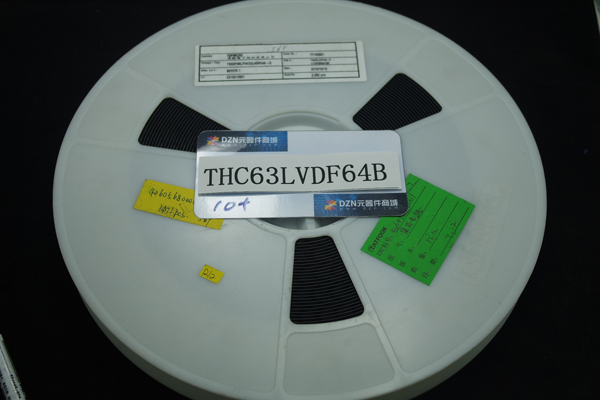

THC63LVDF84B/THC63LVDF64BLVDS 24Bit/18Bit COLOR HOST-LCD PANEL INTERFACE RECEIVER

THC63LVDF84B / THC63LVDF64BLVDS 24位/ 18位颜色HOST-LCD接收机面板接口

The THC63LVDF84B/THC63LVDF64B receiver sup-ports wide VCC range(2.5~3.6V). At single 2.5V sup-ply, the THC63LVDF84B/THC63LVDF64B reducesEMI and power consumption.The THC63LVDF84B receiver convert the fourLVDS(Low Voltage Differential Signaling) data streamsback into 28bits of CMOS/TTL data with falling edgeclock.At a transmit clock frequency of 85MHz, 28bits of RGBdata and 4bits of LCD timing and control data(HSYNC, VSYNC, CNTL1, CNTL2) are transmitted ata rate of 2.3Gbps.Also the THC63LVDF64B receiver convert the threeLVDS data streams back into 21bits of CMOS/TTL datawith falling edge clock.At a transmit clock frequency of 85MHz, 21bits of RGBdata and 4bits of LCD timing and control data(HSYNC, VSYNC, CNTL1, CNTL2) are transmitted ata rate of 1.78Gbps.

THC63LVDF84B / THC63LVDF64B接收器支持VCC范围宽(2.5 ~ 3.6 v)。在单2.5 v sup-ply THC63LVDF84B / THC63LVDF64B reducesEMI和功耗。THC63LVDF84B接收器将fourLVDS(低电压差分信号)数据streamsback为28位CMOS / TTL数据edgeclock下降。在传输时钟频率为85 mhz,28位RGBdata和4位液晶显示时间和控制数据(HSYNC、VSYNC CNTL1,CNTL2)传输ata 2.3 gbps。还THC63LVDF64B接收器将threeLVDS数据流回21位CMOS / TTL datawith下降沿时钟。在传输时钟频率为85 mhz,21位RGBdata和4位液晶显示时间和控制数据(HSYNC、VSYNC CNTL1,CNTL2)传输ata 1.78 gbps。