第1章

设备概述MC9S12XE-家庭1.1简介

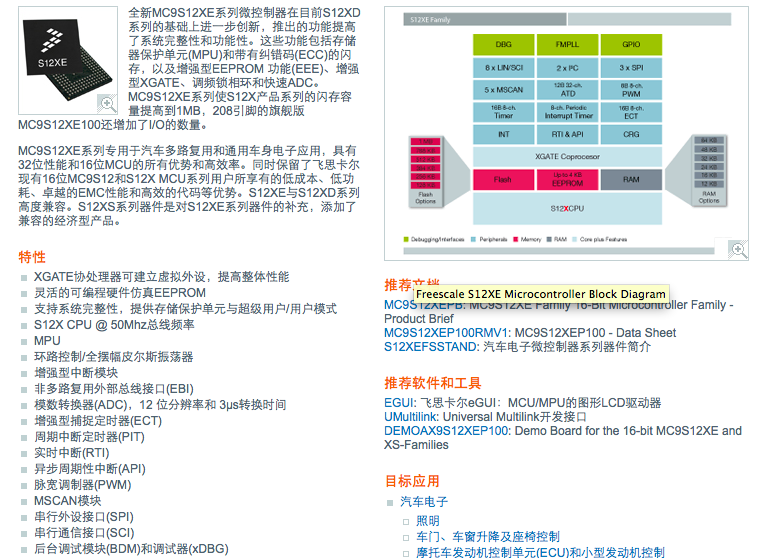

该MC9S12XE-家庭微控制器是S12XD-家庭的进一步发展,包括

新功能增强了系统的完整性和更强大的功能。这些新功能包括:

存储器保护单元(MPU)和纠错码(ECC)的闪存加上

增强了EEPROM的功能(EEE),增强的XGATE,一个内部过滤,频率

调制锁相环(IPLL)和增强的ATD。在E系列扩展S12X产品

在旗舰的208引脚版本范围可达闪存1MB增加的I / O能力

MC9S12XE100。

该MC9S12XE-家庭提供的所有优点和一个16位的效率,32位的性能

MCU。它保留了成本低,功耗小,EMC和代码大小效率目前优势

飞思卡尔现有的16位MC9S12和S12X MCU系列的用户享用。有高水平的

在S12XE和S12XD家庭之间的兼容性。

该MC9S12XE,家庭拥有的性能提升XGATE协处理器的增强版

这是可编程的在“C”语言和运行在S12X的总线频率与一个两倍

指令集的数据移动,逻辑和位操作指令优化,它可以服务

在设备上的任何外围设备模块。新的增强型版本改进了中断处理

能力,并与现有的XGATE模块完全兼容。

该MC9S12XE,家庭是由标准的片上外设,包括高达64K字节RAM,

八个异步串行通信接口(SCI),三个串行外设接口(SPI),一个8

通道IC/ OC增强捕捉定时器(ECT),两个16通道,12位模拟 - 数字转换器,一个8-

通道脉冲宽度调制(PWM),五CAN2.0 A,B软件兼容模块(MSCAN12)

2 IC间总线块(IIC),一个8信道的24位周期中断定时器(PIT)和一个8信道的16位

标准定时器模块(TIM)。

该MC9S12XE-系列使用16位宽的访问,而不等待状态的所有外设和存储器。

非多路复用扩展总线接口上可用二百零八分之一百四十四引脚版本允许容易

接口外部存储器。

除了I /每个模块中提供O端口,多达26个进一步的I / O端口可与中断

功能允许唤醒从停止或等待模式。该MC9S12XE,家庭是提供208-

引脚MAPBGA,144引脚LQFP,112引脚LQFP或80引脚QFP选项。

1.1.1特点

在MC9S12XE,家庭功能列在这里。请参阅表D-2.对于内存选项和表D-

2.外围功能,可在不同的家庭成员。

•16位CPU12X

- 向上兼容MC9S12指令集除5的模糊指示

(MEM,WAV,WAVR,REV,REVW),它已被删除

- 增强索引寻址

- 访问大数据段独立PPAGE的

•INT(中断模块)

- 八个级别的嵌套中断

- 中断源,以每个灵活分配中断级。

- 外部非屏蔽高优先级的中断(XIRQ)

- 内部非屏蔽高优先级存储器保护单元中断

- 多达24个引脚端口Ĵ,H和P配置为上升沿或下降沿触发中断

•EBI(外部总线接口)(208引脚和144引脚仅封装)

- 最多四个芯片选择输出选择16K,1M,2M以及高达4MByte地址空间

- 每个片选输出可被配置以完成交易在任超时之一

这两个等待状态发生器或EWAIT信号的无效的

•MMC(模块映射控制)

•DBG(调试模块)

- CPU和/或XGATE总线具有触杀型或强制类型断点请求监测

- 64×64位的循环跟踪缓冲区捕获变化的流量或存储器存取信息

•BDM(背景调试模式)

•MPU(内存保护单元)

- 8地址地区每个活动计划的任务定义

- 地址范围粒度低至8字节

- 无写入/否执行保护属性

- 在访问冲突不可屏蔽中断

•XGATE

- 可编程,高性能的I / O协处理器模块

- 转会数据或从所有外围设备和RAMwithout CPU干预或CPU的等待状态

- 执行逻辑,转移,算术和位的运算数据

- 可以中断HCS12X CPU信号传输完成

- 触发从任何硬件模块以及从CPU可能

- 两个中断级以服务高优先级任务

- 堆栈指针初始化硬件支持

•OSC_LCP(振荡器)

- 低功耗闭环控制皮尔斯振荡器利用4MHz至16MHz晶振

- 良好的抗噪性

- 利用2MHz至40MHz晶振全挥杆皮尔斯选项

- 跨导大小,以获得最佳的启动保证金典型的晶体

•IPLL(内部过滤,频率调制相位锁相环时钟代)

第1章器件概述MC9S12XE-家庭

MC9S12XE-系列参考手册版本1.25

飞思卡尔半导体29

- 无需外部元件

- 可配置选项扩频以降低EMC辐射(调频)

•CRG(时钟和复位代)

- COP看门狗

- 实时中断

- 时钟监视器

- 快速从STOP自时钟模式唤醒

•内存选项

- 128K,256K,384K,512K,768K和1M字节的FLASH

- 2K,4K字节的EEPROM仿真

- 12K,16K,24K,32K,48K和64K字节RAM

•闪光一般特点

- 64个数据位加8综合征ECC(错误纠正码)位允许单个位失效

校正和双故障检测

- 擦除扇区大小1024字节

- 自动编程和擦除算法

•D-Flash功能

- 高达32 KB的D-闪存与256字节扇区的用户访问。

- 专用命令来控制访问D-闪存比EEE操作。

- 单比特错误校正和在读操作的字中的双位错误检测。

- 自动编程和擦除算法验证和生成ECC奇偶校验位。

- 快速扇区擦除和字编程操作。

- 能够编程最多四个单词的顺序爆破

•取法EEPROM功能

- 自动EEE文件处理使用内部的内存控制器。

- 从D-闪存自动转移有效EEE数据缓冲复位RAM。

- 能够监测未EEE相关缓冲区RAM字的数目离开是

编入D-闪存。

- 能够禁用EEE操作,并允许优先进入D-闪存。

- 能够取消所有未决EEE操作,并允许优先进入D-闪存。

•两个16通道,12位模拟数字转换器

- 8/10/12位分辨率

- 3μs的,10位单转换时间

- 左/右,符号/无符号结果数据

- 外部和内部转换触发功能

- 内部振荡器转换在停止模式

- 唤醒从模拟比较>或<=匹配的低功耗模式

•五MSCAN(每秒1兆比特,CAN2.0 A,B软件兼容模块)

- 五接收和三个发送缓冲器

第1章器件概述MC9S12XE-家庭

MC9S12XE-系列参考手册版本1.25

30飞思卡尔半导体

- 灵活的标识符过滤器可编程为2×32位,4个16位或8×8位

- 四个独立的中断通道RX,TX,错误和唤醒

- 低通滤波器唤醒功能

- 环回自测试操作

•ECT(增强型捕捉定时器)

- 8×16位通道输入捕捉或输出比较

- 16位自由运行的8位精度预分频器

- 16位的模数递减计数器的8位精度的预分频器

- 四个8位或两个16位脉冲累加器

•TIM(标准定时器模块)

- 8×16位通道输入捕捉或输出比较

- 16位自由运行的8位精度预分频器

- 1个16位脉冲累加器

•PIT(周期中断定时器)

- 多达八个定时器,具有独立的超时周期

- 超时期限介于1和224总线时钟周期可选择

- 超时中断和外围触发器

•8 PWM(脉冲宽度调制)通道

- 8通道x8位或4通道x16位脉宽调制器

- 可编程周期和占空比每通道周期

- 中心 - 或左对齐的输出

- 具有广泛的频率范围可编程时钟选择逻辑

- 快速紧急停机输入

•三个串行外设接口模块(SPI)

- 可配置为8或16位的数据大小

•八条串行通信接口(SCI)

- 标准标记/空白不归零(NRZ)格式

- 可选择的IrDA1.4回归到零反转(RZI),具有可编程脉冲宽度格式

•两个IC间总线(IIC)模块

- 多主机操作

- 软件编程一256不同的串行时钟频率

- 广播模式支持

- 10位地址的支持

•片上稳压器

- 两个平行的,线性稳压器与带隙基准

- 低电压检测(LVD),低电压中断(LVI)

- 上电复位(POR)电路

- 3.3V和5V的工作电压范围

- 低电压复位(LVR)

第1章器件概述MC9S12XE-家庭

MC9S12XE-系列参考手册版本1.25

飞思卡尔半导体31

•低功耗唤醒定时器(API)

- 可在所有模式,包括完全停止模式

- 微调至±5%的准确度

- 超时周期范围从为0.2ms到〜13S具有分辨率为0.2ms

•输入/输出

- 最多152个通用输入/输出(I / O)引脚加上2仅输入引脚

- 滞后和可配置的上拉/下拉设备上的所有输入引脚

- 对所有输出引脚配置的驱动力

•封装选项

- 208引脚MAPBGA

- 144引脚小外形四方扁平封装(LQFP)

- 112引脚小外形四方扁平封装(LQFP)

- 80引脚四方扁平封装(QFP)

•最高50MHz的CPU总线频率,100MHz的最大XGATE总线频率

1.1.2工作模式

内存映射和总线接口模式:

•正常和仿真运行模式

- 正常的单芯片模式

- 普通扩展模式

- 单芯片模式仿真

- 扩大模式仿真

•特殊操作模式

- 特殊的单芯片模式与Active后台调试模式

- 特殊测试模式(飞思卡尔只使用)

低功耗模式:

•系统停止模式

- 伪停止模式

- 全面停止模式快速唤醒选项

•系统等待模式

操作系统状态

•主管状态

•用户状态